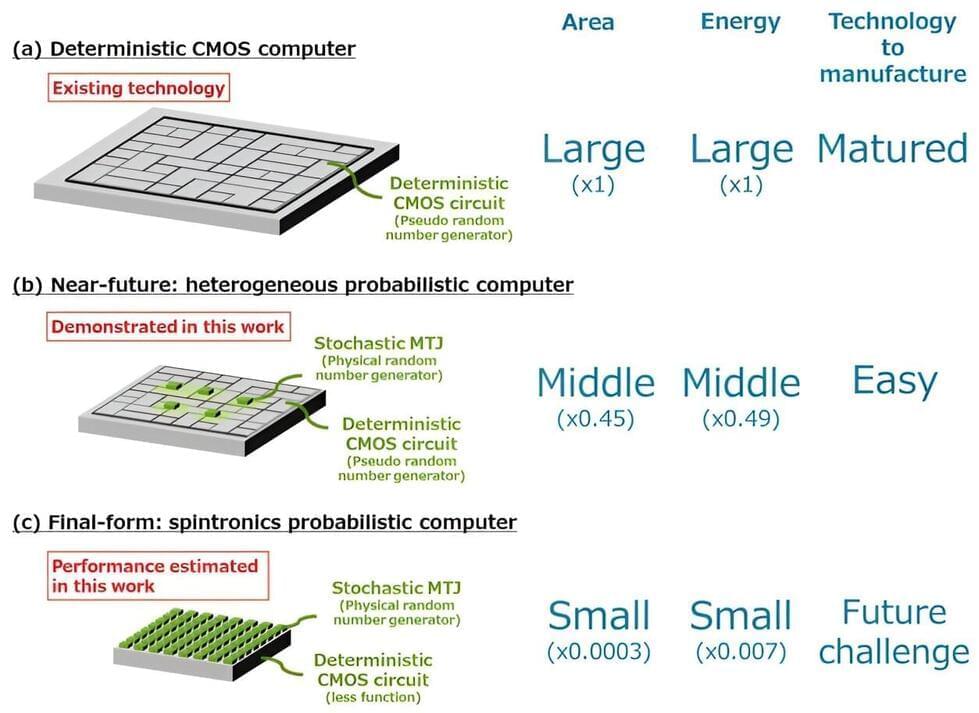

In this study, graduate student Keito Kobayashi and Professor Shunsuke Fukami from Tohoku University, along with Dr. Kerem Camsari from the University of California, Santa Barbara, and their colleagues, developed a near-future heterogeneous version of a probabilistic computer tailored for executing probabilistic algorithms and facile manufacturing.

“Our constructed prototype demonstrated that excellent computational performance can be achieved by driving pseudo random number generators in a deterministic CMOS circuit with physical random numbers generated by a limited number of stochastic nanomagnets,” says Fukami. “Specifically speaking, a limited number of probabilistic bits (p-bits) with a stochastic magnetic tunnel junction (s-MTJ), should be manufacturable with a near-future integration technology.”

The researchers also clarified that the final form of the spintronics probabilistic computer, primarily composed of s-MTJs, will yield a four-order-of-magnitude reduction in area and a three-order-of-magnitude reduction in energy consumption compared to the current CMOS circuits when running probabilistic algorithms.